# **EPFL**

# SUPERCOMPUTING REVIEW

NUMERICAL SIMULATION FOR SCIENCE AND TECHNOLOGY

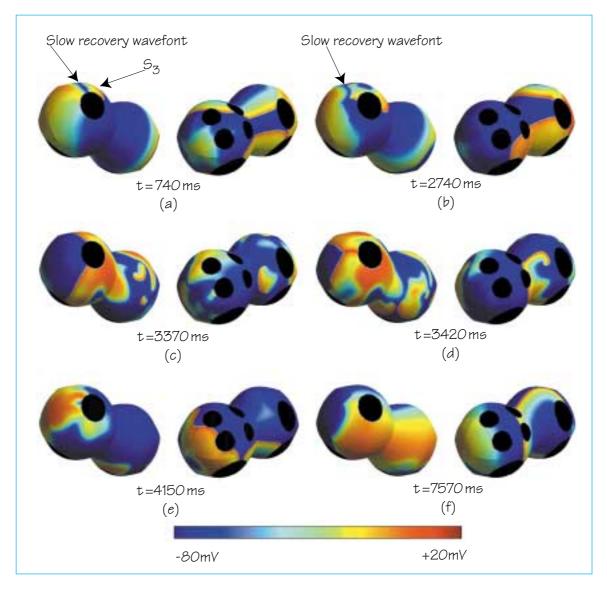

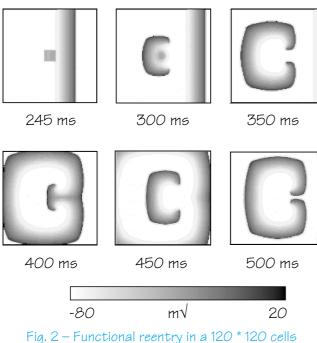

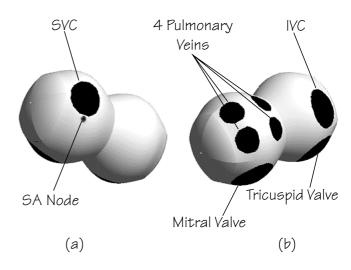

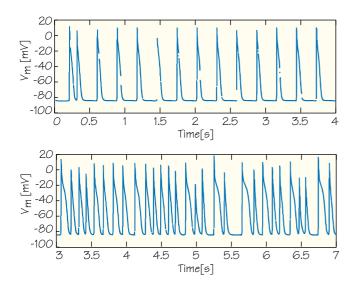

Initiation of a nonsustained atrial fibrillation. First, one normal stimulus is applied followed by two ectopic beats S2 and S3. We can see the evolution of the action potentials: (a) t=750 ms, shortly after the application of S3 which collides with the slow recovery wavefront created by S2; (b) t=2740 ms, just at the onset of atrial fibrillation; (c) t=3370 ms and (d) t=3420 ms show the atrial fibrillation with up to 6 independent wavelets, note the appearance of u-turns and anatomical reentry around veins; (e) t=4155 ms transition between atrial fibrillation and atrial flutter, note the anchoring effect around SVC; (f) t=7570 ms atrial flutter with a periodic pattern. (see article on page 32)

# **Contents** Table des matières

Parallel computer architectures for commodity<br/>computing and the Swiss-T1 machineArchitectures de machines parallèles construites<br/>avec des matériels standardisés et l'ordinateur<br/>Swiss-T1Pierre Kuonen & Ralf Gruber3Communication Libraries for the Swiss-Tx<br/>MachinesLes librairies de communication pour les machines<br/>Swiss-Tr

| 0W135 1X       |    |

|----------------|----|

| Stephan Brauss | 12 |

### Parallel File Striping on the Swiss-Tx Architecture

Entrées/sorties parallèles sur les disques locaux de l'architecture Swiss-Tx

15

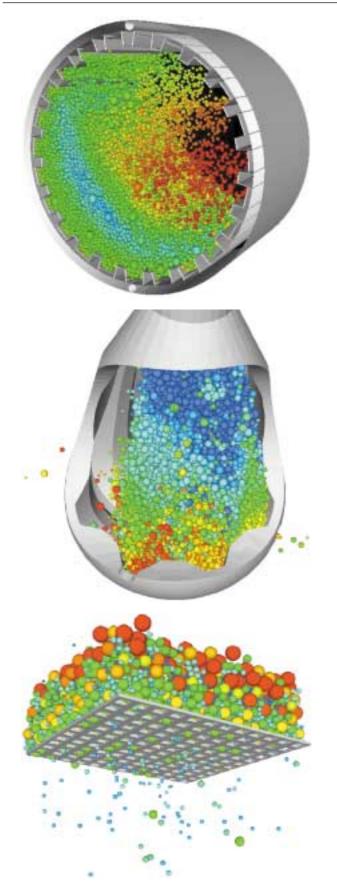

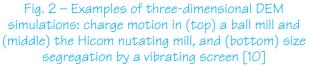

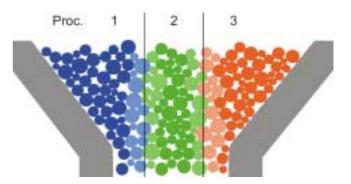

### A Parallel Discrete Element Method for Industrial Granular Flow Simulations

Une méthode d'éléments discrets parallélisés pour les simulations d'écoulements granulaires industrielles

Mark L. Sawley & Paul W. Cleary 23

# Performance test of the SPECULOOS code on the T0-Dual parallel machine

*Test de performance du code SPECULOOS sur l'ordinateur parallèle T0-Dual Daniel Weill* 29

### Computer simulation of atrial arrhythmias

Simulation informatique des arythmies auriculaires

Olivier Blanc, Jean-Marc Vesin, Nathalie Virag, Olivier Egger, Jacques Koerfer & Lukas Kappenberger 32

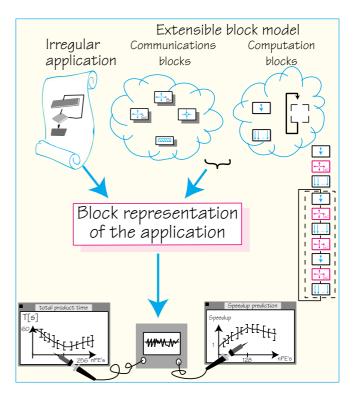

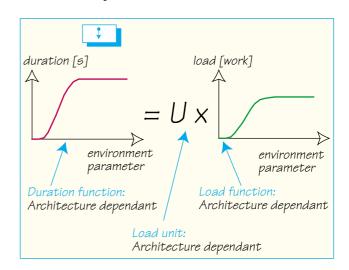

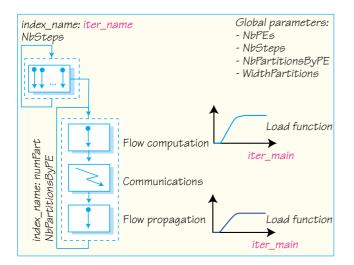

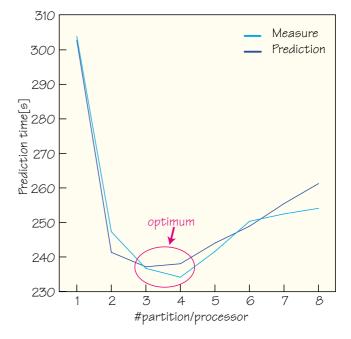

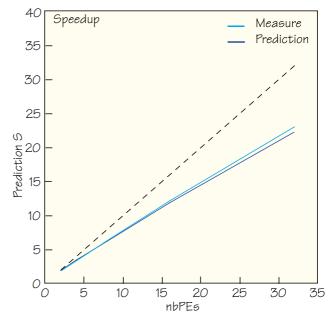

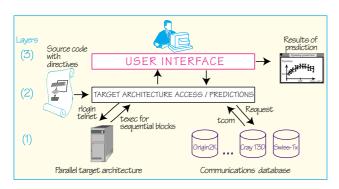

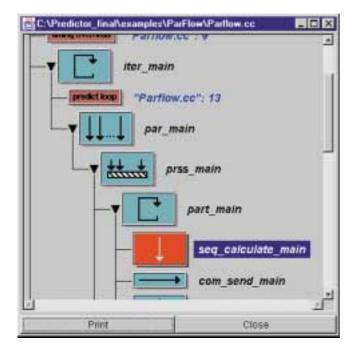

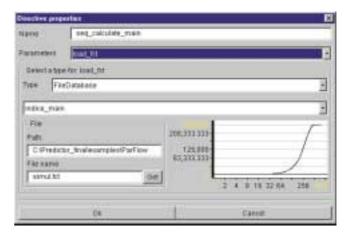

# IP3T a performance prediction tool for irregular parallel programs

IP3T, un outil de prédiction de performance pour applications parallèles irrégulières Michel Pahud 36

> For more information about CAPA: Pour plus d'informations sur CAPA http://capawww.epfl.ch/

# **Editorial**

Depuis quelques années, l'idée d'assembler des machines destinées aux calculs à haute performance à partir de composants standard du marché est devenue attrayante dans la communauté des scientifiques. Ces machines devraient rivaliser en performance avec les super-ordinateurs actuels et offrir un rapport prix-performance plus avantageux. Ce défi a donné naissance à de nombreux projets dans le monde et parmi ces projets, il y a Swiss-Tx dans lequel l'EPFL participe intensivement. En effet, deux machines prototypes sont déjà à l'EPFL et une nouvelle machine pourrait être installée à la fin de cette année (page 3). Bien que les machines Swiss-Tx soient assemblées à partir de stations de travail, elles possèdent néanmoins un réseau de communication développé en Suisse qui supporte une implantation de la librairie standard de communication MPI\* (page 12) et un module NAFS de fichiers répartis utilisé pour les entrées-sorties parallèles (page 15). Les performances de deux des applications tournant sur ces machines sont montrées dans les articles des pages 23 et 29.

Par la nature multidisciplinaire de cette revue, nous vous proposons deux articles qui à notre avis méritent d'être soulignés. Le premier article concerne une simulation informatique réussie des arythmies auriculaires (page 32). Le deuxième article présente un nouvel outil de prédiction de performance pour les applications parallèles (page 36).

# <u>Editorial</u>

Since a few years, building a machine dedicated to high performance computing made of computer commodities became an attractive endeavour for the scientific community. These machines should be as powerful as the existing supercomputers and should have a favourable price-performance ratio. With this challenging goal, many projects started around the world. The Swiss-Tx, in which EPFL has an intensive participation is one of these projects. Two prototype machines are already in use at EPFL and a new machine might be installed by the end of this year (page 3). Although the Swiss-Tx machines are built from commodity elements, they feature a Swiss-made communication network supporting MPI\*, the standard communication library (page 12) and the NAFS striped files package used for parallel Input/Output (page 15). Performances of two applications running on these machines are presented in the two articles on pages 23 and 29.

As a multidisciplinary review, it is worth proposing two unrelated but interesting articles. The first one talks about computer simulation of atrial arrhythmias (page 32) and shows a successful simulation of some phenomena already observed in nature. The second one presents a new performance prediction tool for parallel applications (page 36).

\* MPI: Message Passing Interface (interface pour les échanges de messages)

# PARALLEL COMPUTER ARCHITECTURES FOR COMMODITY COMPUTING AND THE SWISS-T1 MACHINE

Pierre Kuonen, EPFL, Computer Science Department, Pierre.Kuonen@epfl.ch and Ralf Gruber, EPFL, Computer Services, Ralf.Gruber@epfl.ch

La disparition, au cours des dernières années, des principaux constructeurs de superordinateurs parallèles a favorisé l'émergence d'un nouveau concept de machine parallèle basé sur l'assemblage d'ordinateurs utilisant des composants standards, tels des PCs ou des stations de travail, connectés au travers d'un réseau à haut débit et à latence faible. Dans cet article nous présentons et comparons différentes topologies envisagées pour réaliser de tels réseaux et nous justifions le choix de la machine Swiss-T1 que l'EPFL planifie d'installer à fin 1999 dans le cadre du projet Swiss-Tx. L'objectif de ce projet est de réaliser, à l'horizon 2000, une machine parallèle de faible coût délivrant un Teraflop/s.

Commodity parallel computing becomes more and more popular, as the specialised supercomputing companies stop their activity. In this new concept, a user is confronted with a machine built with mass produced fully equipped workstations or PCs which are interconnected through some high speed, low latency network. In this paper, we discuss and compare the different network topologies that are used to cluster those computational units. Then we justify the choice made for the Swiss-T1 parallel commodity computer that may be installed at EPFL by the end of 1999 in the framework of the Swiss-Tx project. Its final objective is to build a low cost, parallel commodity computer delivering one Teraflop/s by the year 2000.

### INTRODUCTION

Since 6 years, most of the supercomputer vendors have been taken over by PC and workstation manufacturers (Cray, Convex), have stopped supercomputing (Intel), or stopped their business (Thinking Machines, KSR). There is no manufacturer now remaining for whom the main business is supercomputing. Users of high performance parallel machines can now choose among vector machines (Cray/ SGI, NEC, Fujitsu) and SMPs (SGI, IBM, Sun, Compaq, HP, Hitachi). Besides the high prices, the vector machines demand data structures different to those chosen in cache based computers as PCs or workstations and the SMP machines with their customised architectures often do not scale with the number of processors. These are major reasons why commodity parallel computing is now considered as an alternate road map towards high performance parallel computing. In this new approach, autonomous, high performance, shared memory computers are connected by an external high-speed network. Global communication between processors can be taken care of by message passing libraries such as MPI. Such parallel computers are often called message passing machines for which a user has to care about optimising the MPI implementation to become efficient on all those computer architectures. In contrary to vector machines, the use of commodity computers as computational units guarantees that local optimisation has not to be touched when porting a PC or workstation program to a commodity supercomputer.

In this paper we first discuss and compare the different popular network architectures chosen to cluster computational units with a special emphasis on circulant graphs. Secondly, we present the Swiss-Tx commodity parallel computer project [2, 3] that aims at delivering a Teraflop machine by the year 2000.

#### **NETWORK ARCHITECTURES**

The definition of efficient interconnection network topology is a major issue of parallel commodity computer designers. Since many years, several topologies have been studied and used to build parallel computers. For example, a few years ago, hypercube topology was largely used because of its apparently low diameter and its good mathematical properties. Besides the SGI Origin2000, this topology is not any more used today because of its lack of scalability. Topologies derived from trees are used in the IBM SP-2 and the fat-tree topology by the Compaq-Quadrics machines using a follow-up of the Meiko [7] network technology. On the other hand, there is a trend towards simple graphs such as grids (often used by Beowulfs) or the torus (SGI/Cray T3E). In the following paragraphs we will present the results of our studies concerning the topologies for interconnection networks realised in the framework of the Swiss-Tx project.

The graph theory is the main mathematical method applied in the field of interconnection networks. To well understand the content of this paper we start with a glossary:

- A graph is made of *edges* and *nodes*;

- The *size* of the graph is the number N of nodes of the graph. It is directly related to the maximum computa-

tional power of the machine. Typically, each node of the graph will be occupied by a fixed number P of processors;

Two nodes are *adjacent* if they are the extremities of the same edge;

EPFL SUPERCOMPUTING REVIEW

- A *chain* between two nodes x and y is a list of k nodes  $x_1,...,x_k$  such that two consecutive nodes  $x_i$  and  $x_{i+1}$ , 0 < i < k, are adjacent and such that  $x_1 = x$  et  $x_k = y$ ;

- A graph is *connex* if there exists a chain between each pair of nodes of the graph. In the following, we are only interested in connex graphs;

- The *length* of a chain is the number of its edges;

- The *distance* d<sub>ij</sub> between two nodes x<sub>i</sub> and x<sub>j</sub> is the length of the shortest chain between them;

- The *diameter D* of a graph is the longest distance in the graph;

- The *average diameter* (or *average distance*) *Dm* of a graph is defined as:

$$Dm = \sum d_{ij} / (N^2 - N)$$

where N is the size of the graph (by definition,  $d_{ii}$ =0). The average diameter influences the transfer time between arbitrary nodes and the diameter influences the time used to broadcast information. In any case we will try to minimise these values with respect to the size and the degree of the graph;

- The *bisectional width BiW* is the smallest number of edges we have to cut in order to separate the graph in two parts of the same number of nodes (plus or minus one). It is an informal measure of the available bandwidth between the two half of the machine. Usually we will try to keep this value as high as possible;

- The *degree d* of a node is the number of nodes adjacent to it. The degree imposes the number of network communication (NC) ports we must have on each node. Usually this number is dictated by the status of the used technology. In any case, the price of the machine increases with the number of needed NC ports;

- A graph is *regular* if all the nodes have the same degree. In order to avoid special-case nodes, regular graphs are our favourite candidates. Special case nodes can become *hot–spots* and increase the contention phenomena;

- A *topology* is a class of graphs;

- A topology is *rigid* if for any given size N and degree d there exists only a few (<<N) graphs of degree d and of size smaller or equal to N. An example of a very rigid topology is the hypercube. There exits only one hypercube with a given degree d and the size of this hypercube must be 2<sup>d</sup>. Therefore, following the above definition, for any d and N there exists at most one hypercube of degree d and of size smaller or equal to N. To build computers of any power we need to have a great liberty on the choice of the size of the graph. Therefore we try to avoid rigid topologies.

To summarise, the ideal topology should have the following characteristics: *It should be regular and not rigid, we need a low average diameter, a low diameter and a high bisectional width for a large size and a small degree.*

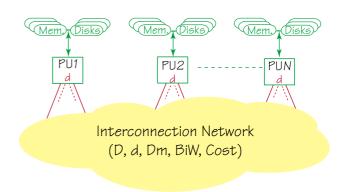

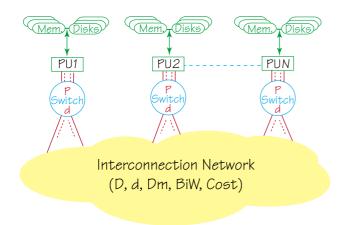

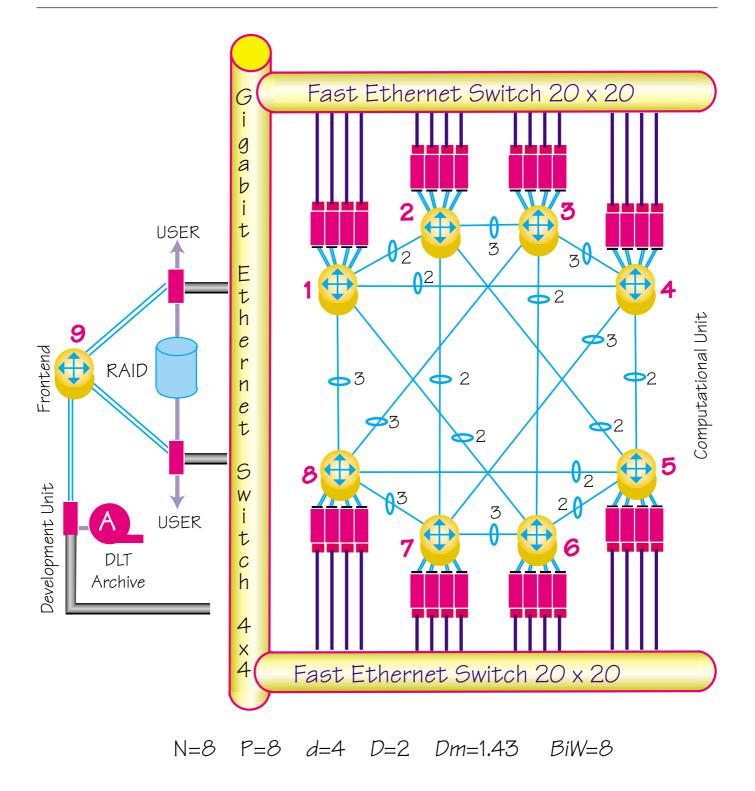

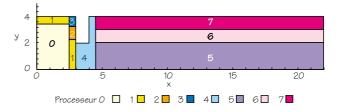

Our objective is to compare different topologies. To do so, we need to define clearly what parameters of which graphs should be compared. As it can be seen in Fig. 1, the processing power of a machine is characterised by the number N of processing units (PU) or nodes as previously defined and the number P of processors per PU, and the network by the degree d, the diameter D, the average diameter Dm, the bisectional width BiW, and the cost. In our study, we will compare graphs with the same number of PUs and processors per node. In others words, the problem is to decide, for a given computing power, which are the topologies having the best connection characteristics.

Fig. 1 – General representation of a commodity parallel computer

# **C**IRCULANT GRAPHS

In [5] we analyse and propose the so-called K-Ring topology for the network of the Swiss-Tx machines. We show that this topology has better characteristics than the most currently used (hypercube, torus, fat-tree,..) ones. In the following section we are going to enlarge our study in order to extend our analysis to a topology called circulant graphs [1] that includes the K-Rings.

• A circulant graph:  $C_N < a_1, a_2, ..., a_K >$  with  $0 < a_1 < a_2 < ... < a_K < (N+1)/2$  is a graph of size N where the nodes are numbered from 0 to N-1 and such that the node i is linked to the nodes  $i \pm a_1$ ,  $i \pm a_2$ ,..., $(i \pm a_K) \mod N$ .

Circulant graphs are regular graphs, but they can be non-connex (example  $C_{12}<2,4>$ ). It has been demonstrated [1] that a circulant graph is connex if  $gcd(a_1,a_2,...,a_k,N)=1$ .

The condition " $\exists$  a<sub>i</sub>, a<sub>j</sub> such that gcd(a<sub>i</sub>,a<sub>j</sub>)=1" implies that gcd(a<sub>1</sub>,a<sub>2</sub>,..,a<sub>k</sub>,N)=1, but the reverse is not true. A simple example is: gcd(6,10,15)=1 but gcd(6,10)=2, gcd(6,15)=3 and gcd(10,15)=5. If we impose that a<sub>1</sub>=1, we obtain:  $\forall$ i, gcd(1,a<sub>i</sub>)=1 and the corresponding graph is connex. Even if the class of circulant graphs having a<sub>1</sub>=1 does not contain all the connex circulant graphs, we will restrict our analysis to circulant graphs having a<sub>1</sub>=1 i.e. to  $C_N < 1,a_2,..,a_K >$ .

It has to be noted that K-Rings are circulant graphs  $C_N < a_1, a_2, ..., a_K >$  such that  $\forall i, gcd(a_i, N) = 1$ . Consequently, K-Rings are included in  $C_N < 1, a_2, ..., a_K >$  (see [4] for details).

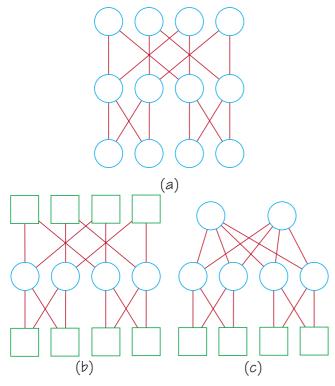

#### FAT-TREES

Fat-tree topology is used to build multi-stage networks. In these networks some nodes of the graph are computing nodes (PU) while other nodes are switching nodes. More details on the fat-tree topology can be found in [6].

Fig. 2(a) present a fat-tree of size 12. Figs. 2(b) and 2(c) presents the two possible solutions for building an interconnection network starting from the fat-tree represented in 2(a). Squares represent computing nodes while circles represent 4x4 crossbar switches. Only computing nodes contain processors. In this paper we will assume that interconnection networks are built using the solution 2(c). This choice is motivated by the fact that fat-trees were designed for maximising the bisectional width. Solution 2(c) leads to a better bisectional width with respect to the number of computing nodes and it is very close to the solution used by Meiko [7].

As it appears in Fig. 2, fat-trees are not regular graphs. Indeed switching nodes have a degree that is the double of the one of computing nodes. In order to compare this topology with a regular one, we have to decide which degree we assume for fat-trees. In order to be fair in our comparison, we base our choice on the degree of the computing nodes. Indeed this degree determines how many NC ports must be present on the PUs. With this hypothesis the graphs presented in Fig. 2 have a degree of 2.

Fig. 2 – Fat-tree of size 12 and the corresponding interconnection networks

#### GRIDS, TORUSES AND HYPERCUBES

Toruses are periodic grids. Since their topologies are well known, we only remind that a torus of dimension K is a regular graph of degree 2K. As our objective is to build the interconnection network of a parallel computer we are not interested by multi-graph (graphs that can have more than one edge between two nodes). More precisely, we consider a multi-graph to be equivalent to the graph obtained by replacing any multiple edges by one edge. With such a definition hypercubes are special case of toruses (toruses of dimension K and of size  $2^{K}$ ).

In the following sections we will compare the characteristics of toruses, fat-trees, and circulant graphs  $C_N < 1,a_2,...,a_K >$ for the same size and the same degree. Our comparisons are limited to the degrees 4, 6, 8 and 10 because, on the one hand, the degree of toruses and circulant graphs must be an even integer and, on the other hand, circulant graphs and toruses of degree 2 are simple rings.

#### COMPARISON OF THE CHARACTERISTICS OF TORUS, FAT-TREES AND CIRCULANT GRAPHS

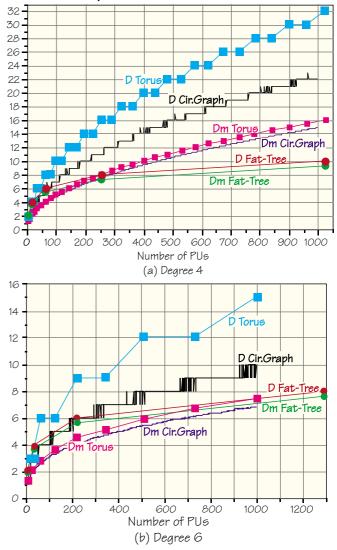

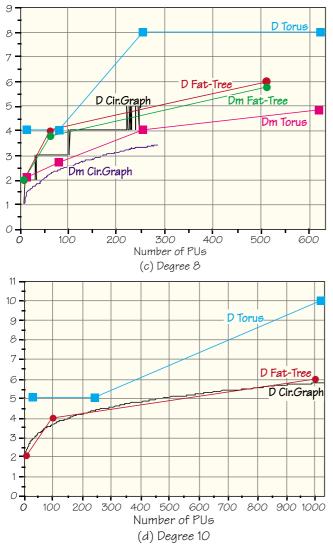

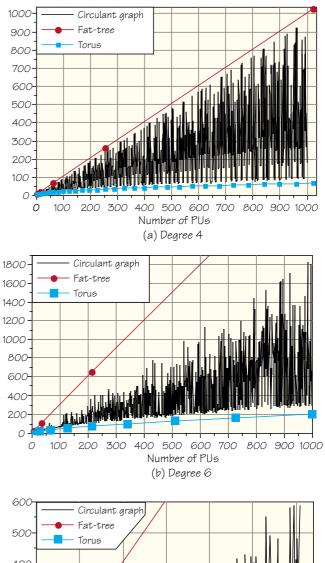

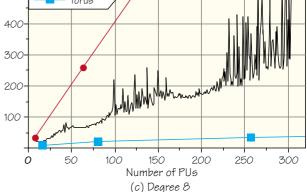

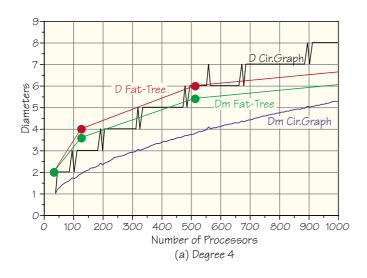

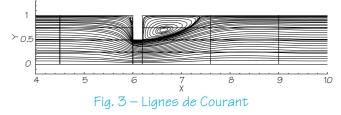

Figs. 3 and 4 presents the comparisons of the measured values of the diameter, the average diameter and the bisectional width for degrees 4, 6, 8 and 10. For degree 10 the values are obtained with an approximate formula, since the computed values were not available for circulant graphs. These results show that:

1. Toruses always have the worst diameter;

Fig. 3 – Comparison of the diameter (D) and average diameter (Dm) of toruses, fat-trees and circulant graphs

- 2. Fat-trees appear to have the best diameter but the difference with circulant graphs is decreasing with increasing degree;

- 3. The average diameter of fat-trees is very close to its diameter, as a consequence, for degrees greater than 4 and a size smaller than 1000, the average diameter of circulant graphs is smaller than the one of fat-trees;

- 4. For a number of PUs up to 1000 the diameter of circulant graphs is smaller or equivalent to the one of fattree as soon as the degree is greater than 6;

- 5. Fat-trees always have the best bisectional width, toruses the worst ones, and the bisectional width of circulant graphs is very erratic.

Based on these results we can discard the toruses that always have the worst diameter and bisectional width. Small degree fat-trees seem to be the best choice even if the difference with circulant graphs is not spectacular. Nevertheless, the drawback of fat-tree is that they are extremely rigid. We have the following properties:

- The number of fat-trees of a given degree d and of size  $\leq N$  is equal to  $\lfloor \text{Log}_d(N) \rfloor$ . For d=8 and N=1000 this number is equal to 3;

- Performant circular graphs can be found for any number of PUs.

In order to decide whether or not fat-trees is a better choice than circulant graphs we are going to study how to build a communication network using these topologies.

#### COMMUNICATION NETWORKS AND CROSSBAR SWITCHES

Fig. 5 – General representation of a parallel computer built using crossbar switches

Recent developments of high-speed crossbar switches have opened new possibilities for the design and the realisation of interconnection networks. Fig. 5 shows the general schema of a communication network built using crossbar switches. In the case of Swiss-Tx machines, the available technology is a 12x12 crossbar switch, called T-NET, designed by the company Supercomputing Systems AG (SCS). The objective of the Swiss-Tx project is to build a parallel machine having a peak performance of up to 1 Teraflop/s. Today's technology can provide processors of a peak performance of 1 Gflop/s (such as the DEC-Alpha 21264). For a parallel one Teraflop/s computer, 1000 one Gflop/s processors have to be interconnected using the high bandwidth, low latency 12x12 T-NET switches. In all the following considerations we make the assumptions that we need one link per processor. This assumption leads to the following possibilities:

- P=2 processors by PU, a topology of degree d=10 and a size of N=500;

- P=4 processors by PU, a topology of degree d=8 and a size of N=250;

- Fig. 6 Diameter (D) and average diameter (Dm) of interconnection networks built using crossbars

- P=6 processors by PU, a topology of degree d=6 and a size of N=167;

- P=8 processors by PU, a topology of degree d=4 and a size of N=125.

All these situations can be realised with circulant graphs; no one can exactly be realised with fat-tree topology.

Fig. 6 compares the diameters of possible solutions using fat-trees and circulant graphs. For degrees 4, 6 and 8 the results are computed values, for degree 10 results are based on an approximate formula. Possible solutions using fat-trees are indicated with a dot. It clearly appears that circulant graphs always have a diameter smaller or equal to the one of fat-trees. Nevertheless, fat-trees have a better bisectional width.

EPFL SUPERCOMPUTING REVIEW

At this stage of our analysis it is still difficult to choose between circulant graphs and fat-trees. Circulant graphs are much more flexible, have most of the time a better diameter and always have a better average diameter whereas fat-trees have a better bisectional width. The last criterion we have to analyse is the cost of the network.

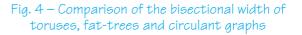

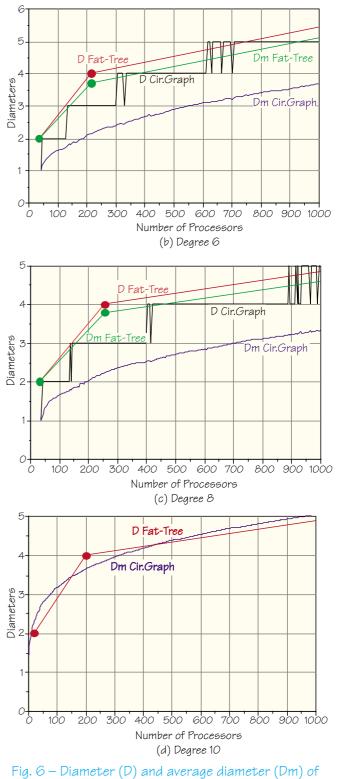

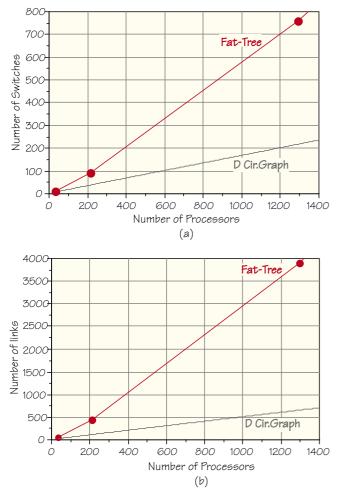

Fig. 7 – Cost of interconnection networks of degree 6 built using 12x12 crossbar switches

The cost of a massively parallel machine is roughly composed of the cost of the PUs and the cost of the communication network. Since N\*P is chosen to be the same in all the cases, the cost for the PUs is the same for fattrees and circulant graphs. The cost of the network is directly related to the number of switches and links necessary to build it. Fat-trees have the following property: if we use nxn crossbars to realise the switch nodes and the computing nodes then the degree of the fat-tree must be n/2 (see Fig. 2). Therefore, if the available technology is 12x12 crossbars, we are limited to a degree of 6.

Fig. 7 shows the cost of fat-trees and circulant graphs of degree 6 for a number of processors up to 1400. The needed links and crossbars increase more rapidly for fat-trees than for circulant graphs. Let us compare possible solutions that are the closest to 1000 processors:

- Fat-Tree: 1296 processors (216 PU's), a diameter of 6, an average diameter of 5.63, a bisectional width of 648, 756 crossbars and 3888 links;

- Circulant graph: 1002 processors (167 PU's), a diameter of 5, an average diameter of 3.68, a bisectional width of 96, 167 crossbars and 501 interconnection links.

Of course the solution with a fat-tree has a much better bisectional width. But two remarks can be made:

- 1. The high bisectional width has its price. Thus, the ratios of the number of switches and links between the fat-tree solution and the circulant graph solution are 4.53 and 7.77, respectively;

- 2. The number of processors in a fat-tree must be a power of 6. Using circulant graphs, the number of processors must be a multiple of 6. Thus, there always exists a solution close to a given number of processors.

Because of their flexibility and of the erratic behaviour of their bisectional width, circulant graphs can always exhibit solutions having a good bisectional width for a number of processors close to a given value. In our case we can mention two possibilities:

- 1. 1260 processors (210 PU's), a diameter of 6, an average diameter of 3.98, a bisectional width of 362, 210 crossbars and 630 links;

- 2. 1356 processors (226 PU's), a diameter of 6, an average diameter of 4.07, a bisectional width of 394, 226 crossbars and 678 links.

Nevertheless, these two solutions still have a quite low bisectional width compared with the one for the fat-tree solution. But, as using circulant graphs we are not limited to a degree 6, we can also build solutions using a circulant graph of degree 8 (with 4 processors on each switch). Doing this we find the following solution:

1192 processors (298 PU's), a diameter of 5, an average diameter of 3.47, a bisectional width of 588, 298 crossbars and 1192 links.

In comparison with the solution of 1296 processors using a fat-tree, this solution exhibits a better diameter and average diameter, uses 2.5 times less crossbars, 3,26 less links and achieves a bisectional width per processor of 0.49 which is almost the same as the fat-tree solution (0.5).

Nevertheless, if the only important parameter is the bisectional width, regardless any other considerations and particularly the cost, we can design the interconnection network using circulant graphs of degree 10 with two processors per PU. Below are the characteristics of some examples of these possible solutions:

- 1000 processors (500 PU's), a diameter of 5, an average diameter of 3.54, a bisectional width of 570, 500 crossbars and 2500 links;

- 1020 processors (510 PU's), a diameter of 5, an average diameter of 3.57, a bisectional width of 642, 510 cross-bars and 2550 links;

- 1080 processors (540 PU's), a diameter of 5, an average diameter of 3.61, a bisectional width of 778, 540 cross-bars and 2700 links.

For these solutions the bisectional width per processor is 0.57, 0.63 and 0.72, respectively, which is better than the solution using a fat-tree. Moreover they use significantly less crossbar switches and links.

As a conclusion we can say that the fat-tree is a topology especially designed for exclusively building very high performance interconnection network. The circulant graph topology allows to adapt the performance of the interconnection network to the user needs and, if needed, it allows to obtain performance equivalent or better to fat-tree for a lower cost. Moreover, the fat-tree topology is a very rigid topology, it cannot fully benefit from the increasing size of the crossbar switch technology, since the degree of a fat-tree must correspond to half of the crossbar size, and the number of PUs must be a power of the degree. With circulant graphs, networks of any numbers of PUs can be built.

For all those reasons we decided to use circulant graphs for building the interconnection network of the Swiss-Tx computers series. In the next section we present the architecture of the Swiss-T1 computer which is based on a circulant graph.

### **Swiss-T1** configuration

#### HARDWARE CONFIGURATION

The first prototype Swiss-T1 machine will consist of 8 PUs connected using the T-NET 12x12 crossbar switches. Each PU consists of 4 dual processor, Alpha-based, DS20 servers, 2 links are used per server, and 8 links per PU (one link per processor). The four remaining links are used to connect the 8 PUs through the circulant graph:  $C_8 < 1,3 >$ (Fig. 8). The diameter is 2, the average diameter is 1.43 and the bisectional width is 8. It has to be noted that we obtain a K-Ring for this particular case. An efficient routing for communications between all PUs is given in Table 1. This table has to be read in the following manner: for a direct link between the nodes, the routing number is identical to the destination node (blue background), for an indirect connection, the number (yellow background), denotes the crossbar number through which the routing passes. In Fig. 8 the numbers on the links indicate the number of packages that have to be sent in both directions for such an all-to-all message passing operation. The routing table has been set up to well distribute the charge on the different links during an all-to-all global communication.

The architecture is completed by a frontend consisting of 2 dual processor DS20 servers. The frontend is con-

nected to the computing nodes through the Gigabit Ethernet/Fast Ethernet switching system.

|   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| 1 | - | 2 | 2 | 4 | 4 | 6 | 8 | 8 |

| 2 | 1 | - | 3 | 7 | 5 | 3 | 7 | 5 |

| 3 | 2 | 2 | - | 4 | 4 | 6 | 8 | 8 |

| 4 | 1 | 7 | 3 | - | 5 | 7 | 7 | 3 |

| 5 | 4 | 2 | 4 | 4 | - | 6 | 6 | 8 |

| 6 | 1 | 3 | 3 | 7 | 5 | - | 7 | 1 |

| 7 | 8 | 2 | 8 | 4 | 6 | 6 | - | 8 |

| 8 | 1 | 5 | 3 | 3 | 5 | 1 | 7 | - |

#### Table 1 – Routing table for the Swiss-T1 machine

- The detailed hardware and software specifications are:

Swiss-T1 consists of 8 PUs, each one including one 12x12 crossbar and 4 Alpha 21264 dual-processor boxes running at 500 MHz, giving 64 Gflops peak performance. One box has 1 Gbytes of main memory and 18 Gbytes of local disk space;

- Each box is connected to the 12x12 crossbar by two bidirectional 100 Mbyte/s links through PCI adapters;

- Four links interconnect the crossbars. The communication configuration is the circulant graph  $C_8 < 1,3 >$ ;

- For an all-to-all communication, up to three messages in both directions have to be sent between crossbars if one follows the routing table given in Table 1;

- There is one frontend node consisting of 2 Alpha 21264 dual-processor boxes running at 500 MHz. Each box includes 2 Gbytes of main memory and 18 Gbytes of local disk space. During the installation phase it will be connected only through the Gigabit Ethernet/Fast Ethernet switching system, in a second phase, it will be directly linked to the T-NET as well;

- Two 20x20 Fast Ethernet switches interconnect the upper and lower half of the computational boxes;

- A RAID disk system of 300 Gbytes is connected to the frontend;

- The remaining frontend crossbar links can be used to interconnect other units;

- There is also a development box identical to a compute box separated from the production machine;

- A one Terabytes archive robot system is connected to the development box.

#### SOFTWARE CONFIGURATION

The different important software packages to be installed on the Swiss-T1 are (the programs marked with \* will be available at T1 installation time):

Fig. 8 – Swiss-T1 architecture based on Alpha 21264 dual-processors. The 8 PUs consist of 4 dual processor boxes. They are connected by a 12x12 crossbar switch, called T-NET. Each box, represented by a red rectangle, is connected by two links, the remaining 4 links connect to other crossbars. The diameter is D=2. For an all-to-all communication 3 bidirectional data exchanges are needed at most. The numbers on the links denote the number of these exchanges between these links. A Gigabit Ethernet/Fast Ethernet switching system directly connects the boxes to the frontend. An archive robot of 1 Tbytes and a RAID disk can be accessed by the 2 frontend boxes in a symmetric manner. There is a special development machine connected to the Fast Ethernet and the Gigabit Ethernet.

#### BASIC SOFTWARE IN EACH DUAL PROCESSOR BOX

| *Tru64 Unix    | Compaq         | Operating system in each box       |

|----------------|----------------|------------------------------------|

| *F77/F90       | Compaq         | Fortran compilers                  |

| *HPF           | Compaq         | High performance Fortran           |

| *C/C++         | Compaq         | C and C++ compilers                |

| *DXML          | Compaq         | Digital math library in each box   |

| *MPI           | Compaq         | SMP message passing interface from |

|                |                | Compaq (only usable in a box)      |

| *Posix threads | Compaq         | Threading in a box                 |

| *OpenMP        | Compaq         | Multiprocessor usage in a box      |

|                |                | through directives                 |

| *KAP-F         | Kuck Ass. Inc. | To parallelise a Fortran code in a |

|                |                | multiprocessor box (preceeds       |

|                |                | OpenMP)                            |

| *KAP-C         | Kuck Ass. Inc. | To parallelise a C program in a    |

|                |                | multiprocessor box (preceeds       |

|                |                | OpenMP)                            |

|                |                |                                    |

Software to pass messages between the boxes and to use them in parallel

| *LSF       | Platform/ | Load Sharing Facility for             |

|------------|-----------|---------------------------------------|

|            | SIC-EPFL  | resource management                   |

| Monitor    | SIC-EPFL  | Monitoring of system parameters       |

| *Totalview | Dolphin   | Parallel debugger                     |

| *Paradyn   | Madison/  | Profiler to help parallelising        |

|            | CSCS      | programs                              |

| *MPI-1/FCI | SCS AG    | Message passing interface between     |

|            |           | boxes running over T-NET              |

| MPI I/O    | SCS/      | Message passing interface             |

|            | LSP-EPFL  | for I/O                               |

| *MPICH     | Argonne   | Message passing interface running     |

|            |           | over Fast Ethernet                    |

| *PVM       | UTK       | Parallel virtual machine running over |

|            |           | Fast Ethernet                         |

| *BLACS     | UTK       | Basic linear algebra subroutines      |

| *ScaLAPACK | UTK       | Linear algebra matrix solvers         |

| NAG        | NAG       | Math library package                  |

| MEMCOM     | SMR SA    | Data management system for dis-       |

|            |           | tributed architectures                |

#### **C**ONCLUSIONS

The fat tree topology was especially designed to build a very high bandwidth network. As the fat-tree is a topology derived from trees, the diameter grows optimally with the logarithm of the number of PUs. The drawback of this topology is the extreme rigidity, the high cost, i.e. the very high number of links and switches.

We expect, but we have not proven yet, that the diameter of circulant graphs grows as  $\frac{d}{\sqrt{N}}$  which is, on a theoretical point of view, not as good as fat-trees. Nevertheless, due to its great flexibility we can fully benefit from the numerous possibilities offered by the use of the crossbar technology. Consequently, in the practice, it is always possible to find a solution using circulant graphs which have better characteristics for a lower cost than the ones using fat-trees. Moreover, by using circulant graphs we can adapt the performance of the network to user needs. For a given number of processors and a given crossbar switch technology, we can choose the performance of the network. If, subsequently, the user needs to increase this performance we can increase the degree of the circulant graph without changing the number of processors. The opposite modification is also possible, we can increase the number of processors without changing the degree of the circulant graph. This flexibility which is not possible with other topologies, allows us to optimise the ratio price/performance according the user needs.

#### ACKNOWLEDGEMENTS

We would like to thank Martin Frey for continuous interaction to define the Swiss-T1 architecture and to Mario Romano for the graphical representation of it. The Swiss-Tx project is a co-operation between EPFL, ETHZ, CSCS, Supercomputing Systems and Compaq. It is financed by CTI (Commission for Technology and Innovation at Bern).

#### REFERENCES

- [1] F.Boesch, R. Tindell, *Circulants and their Connectivities*, Journal of Graph Theory, vol 8, p.487-499, 1984

- [2] S. Brauss, M. Frey, A. Gunzinger, M. Lienhard and J. Nemecek, *Swiss-Tx Communication Libraries*, HPCN'99 (Amsterdam) and this issue

- [3] Y. Dubois-Pèlerin, R. Gruber and Swiss-Tx Group: Swiss-Tx, First experiences on the TO system, EPFL, Supercomputing Review, 10 (1998) 19-23 and http://capawww.epfl.ch/

- [4] P. Kuonen: *The K-Ring*, Proceedings of the European Research Seminar on Advances in Distributed Systems (ERSADS), April 1995.

- [5] P. Kuonen, R. Gruber, A. de Vita and P. Volgers, *Parallel computer architectures for commodity computing*, keynote lecture at High Performance Computing and Networking (HPCN) Europe, Amsterdam, April 12-14, 1999

- [6] Leiserson C.E. Fat-Tree, Universal network for hardwareefficient supercomputing, IEEE Transactions on Computers, C-34, No. 10 (1985) 892-901

- [7] *Communication Network Overview*, http://www.meiko.com/ info/NetworlOverview/Network/Overview.html.

# Communication Libraries for the Swiss-Tx Machines

STEPHAN BRAUSS, SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH (ETHZ), BRAUSS@IFE.EE.ETHZ.CH

Dans le projet Swiss-Tx, les composantes matérielles et logicielles pour la communication sont développées spécifiquement, car les produits standard disponibles ne peuvent pas offrir une latence, une bande passante, la fonctionnalité et la portabilité nécessaires. Une implémentation complète de MPI, standard pour les librairies des échanges de messages, est disponible. Elle est basée entièrement sur la nouvelle interface de communication rapide, Fast Communication Interface (FCI). Cet article montre le concept de communication utilisé dans le projet Swiss-Tx incluant les librairies FCI et MPI. Il compare ensuite cette librairie MPI avec MPICH, une implémentation disponible gratuitement.

In the Swiss-Tx project, the communication hardware and communication software are custom-made, because available standard products do not offer the necessary bandwidth, latency, functionality, and portability. A full implementation of MPI, the standard for message-passing libraries, is available. It is designed entirely on top of the new Fast Communication Interface (FCI). This paper presents the Swiss-Tx communication concept including FCI and MPI and compares Swiss-Tx MPI with the freely available implementation MPICH.

### INTRODUCTION

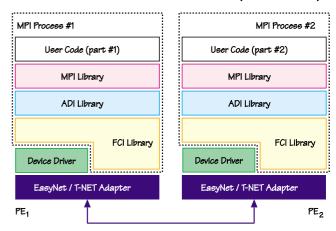

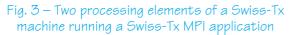

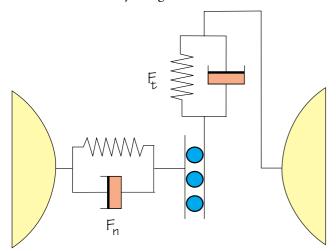

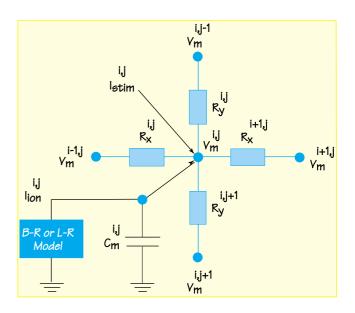

The highlights of the Swiss-Tx communication libraries are low-latency, high-bandwidth, portability, and compatibility. Portability means that all libraries run on various hardware platforms (currently PCs and Compaq Alphabased Workstations and Servers), communication networks (currently EasyNet and T-NET<sup>1</sup>) and operating systems (currently Compaq Tru64 UNIX, Linux, and Microsoft Windows NT). Compatibility means that user programs run without any modification on different platforms. For this reason, a high-level communication library offering the standardized Message Passing Interface (MPI) [3] is available. This MPI library is written entirely on top of the so-called Fast Communication Interface (FCI) [2]. See Fig. 1 for an overview of the communication hardware and software that is involved when a Swiss-Tx MPI application runs on two processing elements<sup>2</sup>. The MPI application consists of two MPI processes running on two processing elements named PE1 and PE2. Each process consists of the application code (User Code) or a part of it and the communication libraries (that are the same on each processing element). Mainly, the following three libraries are involved:

- Message Passing Interface Library (MPI Library);

- Abstract Device Interface Library (ADI Library);

- Fast Communication Interface Library (FCI Library).

# Fig. 1 – A Swiss-Tx MPI application running on two processing elements

The MPI library offers the high-level MPI routines, the ADI library does a part of the memory management and handles MPI data types. The FCI library is an implementation of the new communication architecture FCI. It offers two programming paradigms: Message Passing and the socalled Remote Store (for an introduction to Remote Store see [6]). The EasyNet or T-NET Communication Adapter is mainly controlled by FCI. The device driver is only used for startup and maintenance purposes and is easy to implement.

### PORTABILITY

Portability is mainly attained by a good overall hardware and software concept and by smart programming. In this concept, we separate the hardware and operating system dependent from the hardware and operating system independent software parts. Most dependencies are covered by the new Fast Communication Interface FCI that is split into the following three interfaces:

API (Application Programming Interface) FCI defines the set of routines which can be used by a

<sup>2</sup> in Swiss-T0, each box has one processing element, in Swiss-T0-Dual a box has two of it [1]

<sup>1</sup> EasyNet is the communication network used in Swiss-T0 and Swiss-T0-Dual, T-NET is used in Baby T1, Swiss-T1, and maybe also in Swiss-T2

parallel application. Such a parallel application can be a pure FCI application (using only the routines offered by the FCI library) or a MPI application with the ADI and MPI libraries (see Fig. 1).

- DDI (Device Driver Interface) FCI defines the functionality that must be offered by the network device driver residing in the kernel.

- NHI (Network Hardware Interface)

FCI defines the functionality of the network hardware.

This includes mandatory and optional parts which can be added for better performance.

FCI guarantees that it is easy to port the communication libraries to new hardware and software platforms, which is a big advantage: We can reuse most of our software which reduces costs and development time:

- Replacing the communication hardware by a new one only affects the network device driver and some low level routines in the FCI library that directly control the communication interface adapter.

- Replacing the platform by for example Motorola Power PC based systems with Apple Mac OS only affects the network device driver (that has to be rewritten once for the new platform with the new operating system) and some low level routines in the FCI library that use the operating system and the device driver.

- Updating the operating system to a new release (for example to Compaq Tru64 UNIX V5.0) or replacing the hardware platform by a new one of the same architecture (for example a migration from Compaq Alpha 21164 Workstations to Compaq Alpha 21264 Workstations) normally needs no modification at all or only affects some small parts in the network device driver.

# Why should I use Swiss-Tx MPI instead of MPICH on a Swiss-Tx machine?

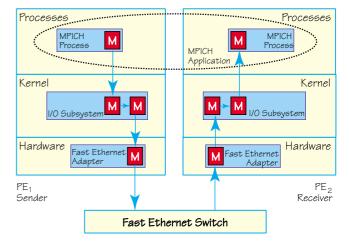

To make you understand why the Swiss-Tx communication libraries perform better than other products, we will compare MPICH [4] on the Swiss-Tx machines with Swiss-Tx MPI. MPICH is a freely available, portable implementation of MPI (Message Passing Interface) [3], the standard for message-passing libraries. On the Swiss-Tx machines, it uses the socket interface with Fast Ethernet to transfer data between processes running on different boxes (see [1]).

In Fig. 2 you can see a MPICH application running on two Swiss-Tx processing elements named  $PE_1$  and  $PE_2$  in a Compaq Tru64 UNIX environment.  $PE_1$  wants to send a message to  $PE_2$ . The message is represented by a rectangle with a letter M inside. At the beginning, the message is held in the MPICH process on  $PE_1$ . When a transfer takes place, the message is copied into the I/O subsystem, which is a part of the UNIX kernel. Additional overhead of the TCP/IP protocol (e.g. the message has to be split up in smaller network packets and the network packets have a checksum that must be calculated in software) is illustrated by another copy step in the I/O subsystem, that is followed by a transfer of the network packets to the Fast Ethernet Adapter. This adapter is a device in a PCI slot of the Compaq Alpha Workstation. The packets are transmitted to the adapter that is located in a PCI slot of PE<sub>2</sub> (by use of a Fast Ethernet Switch) and are stored in a block of memory in the I/O subsystem, where an additional copy step illustrates additional overhead of the TCP/IP protocol. At last, the MPICH process on PE<sub>2</sub> receives the message. Transferring data into the kernel and back to the MPICH process is a resource intensive job: The application has to call a routine in the kernel to initiate such transfers. As you can see, there are three main drawbacks of MPICH on the Swiss-Tx machines:

- messages have to be copied many times;

- the kernel is involved in the transfer of the messages (send and receive) and has to be called therefore;

- the big TCP/IP protocol overhead.

Fig. 2 – Two processing elements of a Swiss-Tx machine running a MPICH application

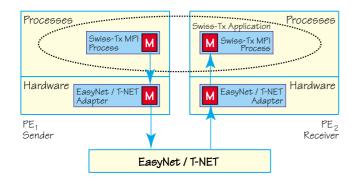

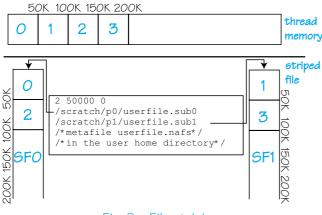

In Fig. 3 you can see a Swiss-Tx MPI application running on the same two processing elements  $PE_1$  and  $PE_2$ as shown above. We are still in a Compaq Tru64 UNIX environment and  $PE_1$  wants to send a message to  $PE_2^3$ . As before, the message is represented by a rectangle with a letter M inside. When the message must be transmitted from  $PE_1$ to  $PE_2$ , it is directly transferred from the Swiss-Tx MPI process on  $PE_1$  to the Swiss-Tx Network Adapter (currently EasyNet or T-NET) that resides in a PCI slot of the Compaq Alpha Workstation. This adapter sends the message to the destination adapter from where it is directly copied to the right location in the Swiss-Tx MPI process on  $PE_2$  by the adapter itself. No CPU time is used to receive the message.

The Swiss-Tx FCI library avoids expensive kernel calls and avoids message copying. Send and receive operations are zero-copy. In addition to that, it has only a small protocol overhead. This can be achieved by an intelligent communication hardware that supports automatic multicast

<sup>3</sup> Assumptions: the message is 4 Byte aligned, contiguous, and transmitted by a blocking send

capable routing <sup>4</sup> and that guarantees secure data transmission which makes error handling in the FCI library unnecessary. All this advantages result in a better overall performance for real applications. A workstation cluster connected by Fast or even Gigabit Ethernet using TCP/IP can also offer reasonable bandwidth and latency. But often, one aspect is not taken into account: Such clusters waste a lot of CPU time for the communication between the processing elements because each processing element has to copy the message several times, has to call routines in the kernel, and has to run the TCP/IP. This time is lost and cannot be used for calculations. These networks often don't reach the possible peak bandwidth at all because the processing elements do not have enough CPU power.

# INSIGHTS INTO THE SWISS-TX COMMUNICATION NETWORKS EASYNET AND T-NET

Transferring messages directly from user space to the communication adapter in a UNIX environment requires that the communication hardware is specifically designed. The same is true for the automatic reception of messages, the Remote Store Concept [6], and other features. In fact, the communication adapters EasyNet and T-NET comply with the so-called Network Hardware Interface (NHI) Specification. This specification includes functionality that is mandatory to implement and other that is optional. Three important parts are the communication channels, the multicast capability and the page table support.

### **COMMUNICATION CHANNELS**

One of the optional features is the number of supplied communication channels that are available on the communication hardware. Depending on the number of such channels, it is possible to attach one or more processes of an application to a communication adapter. Each process needs a private channel and is exclusively bound to this channel. Each process of a parallel application using the Swiss-Tx communication libraries should normally run on a private processing element using a private channel of a communication adapter. EasyNet has only one channel, T-NET is designed to have several, but only one has been implemented yet. This is why only one process per box can use Swiss-Tx MPI on Swiss-T0-Dual. This machine has only one EasyNet adapter per box but each box has two processing elements. On Baby T1, each box has currently two 1-channel T-NET communication adapters, one for each processing element and therefore it is possible to run one process of a Swiss-Tx MPI application on each processing element. It is currently not possible to attach processes of different parallel applications to different channels of the same communication adapter. This restricts how the machine can be partitioned.

In the near future, T-NET will offer an additional channel that is reserved for the operating system. This channel is not part of the NHI. It can be used to transfer TCP/IP packets that are currently transported by Ethernet. This will speed-up applications like PVM [5], NFS [8], and MPICH.

# MULTICAST CAPABILITY

An important feature of T-NET is the possibility to transport multicast messages. It is not fully implemented in the EasyNet hardware. Multicast means that a message can be sent from one communication adapter to a set of receiving adapters. The Swiss-Tx FCI library requires that the message is automatically copied to the right main memory locations of the receiving processing elements without any CPU interaction. This speeds up all collective routines in MPI significantly and reduces the network load.

# T-NET PAGE TABLE SUPPORT

On Swiss-T0, Swiss-T0-Dual, and Baby T1 in the first phase, a programmer has to use the CMM Memory Manager for allocating memory suitable to store data that should be communicated to get the best possible performance. This will be obsolete in the near future. Modern operating systems use virtual memory with techniques called Paging and Swapping. The physical memory is partitioned into a set of pages of equal size that can be assigned to different processes. A process sees a contiguous virtual address space but the physical memory behind this addresses is located in distributed pages of physical memory or is even unallocated. This is managed by software and by the Memory Management Unit (MMU). So it is not guaranteed that a message that is larger than one page is located contiguously in physical main memory. It is even not sure that it is in main memory at all because it could have been swapped out to disk. See [7] for further explanations about Paging and Swapping. Because the communication adapters EasyNet and T-NET store received messages directly into the memory of a dedicated process, three solutions are possible:

- all main memory accesses of the communication adapter are routed through the MMU;

- the operating systems guarantees that the physical block of memory where the messages should be stored is contiguous;

- the communication adapter knows the page tables of the processes it is attached to and translates virtual addresses to physical addresses by itself.

<sup>4</sup> not fully available in EasyNet

The first solution is platform dependent. It assumes that accesses from the communication adapter are routed through the MMU. Using this feature makes us incompatible to a large number of modern platforms. The second solution is implemented in EasyNet and also in the first release of T-NET. The CMM Memory Manager runs in a preallocated area of contiguous main memory that is marked as nonswappable. All memory allocated by this manager is taken out of this area. Such a memory block is guaranteed to be contiguous and available in the physical memory so that the communication adapter is capable to write to it. In the future, T-NET will offer page table support to be as flexible as possible. Memory allocation by the CMM Memory Manager won't be necessary anymore. It is still necessary that pages are fixed in main memory to prevent them from being swapped to disk. This is no real drawback. Applications running on a Swiss-Tx machine should not swap at all because swapping applications has normally a very bad performance.

# Conclusions

The Swiss-Tx communication architecture guarantees that only a small overhead is included by the communication libraries and the communication network. Measurements on an experimental system based on two Compaq Alpha 21264 Workstations equipped with a non-optimized T-NET network are already available. The Swiss-Tx MPI latency is less than 20  $\mu s$  and the bandwidth more than 50 MB/s (theoretical peak bandwidth of the network is 100 MB/s)  $^5$ . Both numbers will be improved.

### REFERENCES

- [1] Swiss-Tx Architecture. Swiss Federal Institute of Technology Lausanne (EPFL), http://capawww.epfl.ch/swiss-tx/index.html

- [2] S. Brauss, J. Nemecek: *The FCI Reference Manual*. Swiss Federal Institute of Technology Zurich (ETHZ), *http:// www.ife.ee.ethz.ch/hpc/fci*

- [3] MPI: A Message-Passing Interface Standard. University of Tennessee, http://www.mcs.anl.gov/mpi/index.html

- [4] MPICH A Portable Implementation of MPI. University of Tennessee, http://www-unix.mcs.anl.gov/mpi/mpich/

- [5] *PVM: Parallel Virtual Machine*. Oak Ridge National Laboratory, *http://www.epm.ornl.gov/pvm/pvm home.html*

- [6] S.Brauss, M.Frey, M. Lienhard, J.Nemecek, A. Gunzinger: Swiss-Tx Communication Libraries. Lecture Notes in Computer Science 1593, HPCN Europe 1999 Proceedings, Springer (1999)

- [7] A. Tanenbaum: Operating Systems: Design and Implementation, pages 191-250, Prentice-Hall (1987)

- [8] NFS: Network File System Protocol Specification. Sun Microsystems, RFC1094, http://www.cis.ohio-state.edu/ htbin/rfc/rfc1094.html

- 5 This measurements have been done at Supercomputing Systems AG in July 1999

# PARALLEL FILE STRIPING ON THE SWISS-TX ARCHITECTURE

BENOIT A. GENNART, EMIN GABRIELYAN, ROGER D. HERSCH, EPFL-DI, PERIPHERAL SYSTEMS LAB. http://visiblehuman.epfl.ch

La tendance actuelle dans le domaine des superordinateurs est de prendre avantage de l'augmentation constante et rapide de la puissance de calcul des stations de travail, et de créer des superordinateurs en empilant des stations de travail et des PC en les connectant par un réseau rapide. Cette approche minimise le coût du matériel en prenant avantage de l'effort de développement des composants grand-public (microprocesseurs, cartes réseau, disques).

Elle pose aussi de nouveaux problèmes : le modèle de programmation, les entrées/sorties, la gestion des utilisateurs et des tâches. Cette contribution discute les problèmes de conception d'un système d'accès aux données sur les ordinateurs à haute performance. Elle présente brièvement l'architecture matérielle, et les raisons de choisir un modèle de programmation distribué. Elle explique en détail la conception et l'implantation du module NAFS de fichiers zèbrés (striped files), dont l'implémentation est fondée sur le langage d'extension CAP. The current trend in the area of high performance computing is to take advantage of the constant and rapid increase in the processing power of desktop workstations, and create supercomputers by piling up workstations and connecting them up with a highspeed network. Such an arrangement ensures minimal hardware cost by taking advantage of the development effort of commodity components (microprocessors, network cards, disks). It also raises new issues: the programming interface, input/output, user and job scheduling.

This paper presents the design issues surrounding input/output to disk on high-performance machines. It presents briefly the basic hardware architecture, and the reasons behind the choice of a distributed memory programming model. It also explains the reasons for offering an interface to distributed scalable data storage. It then describes in detail the design and implementation of the NAFS striped file package, based on the CAP parallel programming extension to C++.

# INTRODUCTION

The current approach to high-performance computing is to use the available computing power in existing workstations and PCs and provide to users tools to extract the best performance out of multiple connected desktop computers. Low-end solutions simply consists of dividing a large task into multiple independent jobs, and submitting them to remote computers, as in the SETI@home project (*http:// www.setileague.org/general/setihome.htm*). Higher-end solutions, for problems with more data dependencies, consists of improving the connectivity of an existing computer network, by using for example an Ethernet crossbar switch. Top-end solutions would include piling up dedicated computers and connecting them through a high-speed custom network, and adding a high-speed archive to handle large data sets.

While it is fairly easy to harness the computing power of multiple desktop computers connected through crossbar switches, achieving a high I/O throughput remains elusive. Solutions involving multiple RAID servers are possible, but involve additional costs. It is therefore tempting to use internal desktop-workstation disk-drives to mimic a single high-performance archive. The principle is to divide user files into multiple subfiles allocated on different disks in each desktop workstation. A parallel-striped-file software package ensures that the multiple files appear to the user as a single conventional file.

The main design goals of a parallel-striped-file package are portability and scalability. Portability is required to ensure that as many available computers as possible can be used regardless of their operating system and network, and leads to the selection of the most common network protocol, namely sockets. Scalability guarantees that the performance of the parallel striped-file package increases as computers are added to the architecture. Achieving highperformance in an I/O system is notoriously difficult: the latency of individual drives is high, and the program I/O operations tend to have small granularity. To improve the performance of the package, it is necessary to design an interface which allows multiple computers to coordinate their I/O activities in what is called collective operations.

Other design goals of a parallel-striped-file package are reliability, transparent job-scheduling, and client-server design. In terms of reliability, it is important for striped-files to survive the crash of a single computer/disk in the parallel architecture. Parallel I/O performance is also very dependent on the location of the files accessed by a program. A smart job-scheduler should be capable of scheduling jobs and moving striped files automatically so as to ensure maximum overall performance. In distributed systems, multiple user programs may access the same file. While this approach is required in the case of e.g. databases, it is often an overdesign in the case of high performance computing, where a single user completely controls the machine (or part of it) and the required files for the duration of the computation. At this point in the project, the reliability, transparency and client-server goals are secondary, and the main focus is on portability and scalability.

This paper describes NAFS, a parallel-striped-file package running under UNIX and WindowsNT.

- The Swiss-Tx hardware architecture and I/O requirements describes the Swiss-TX architecture and its effect on the I/O design;

- The CAP Computer-Aided Parallelization tool describes the precursor to the NAFS striped-file package project, the Visible Human Slice Server;

- **The Swiss-Tx I/O software design** addresses the issues surrounding the design and implementation of the NAFS striped-file package.

### THE SWISS-TX HARDWARE ARCHITECTURE AND I/ O REQUIREMENTS

### HARDWARE ARCHITECTURE

Fig. 8 in article: *Parallel computer architectures* for commodity computing and the Swiss-T1 machine (see on page 3) describes the parts of the Swiss-T1 architecture relevant to the I/O subsystem design. This machine consists of 8 processing nodes, each with 4 dual processor boxes, altogether 64 production processors, and of a four processor front-end subsystem. The front-end subsystem takes care of resource management and of all the external interactions. Two RAID servers connected to the front-end subsystem store the user files. They provide performance through striping and reliability through data redundancy. Each dual-processor box incorporates two 9GB disks, for system and scratch files. The boxes are connected through Ethernet for startup and system messages and through T-Net for high-speed transfers between user processes.

The issues to be addressed in the design of the Swiss-Tx architecture are: performance, scalability, reliability, portability. Performance of a N-processor architecture must be very close to N times the performance of a single processor, otherwise it is very difficult to justify the increase in size of the architecture. The architecture must be able to survive the failure of one or more nodes. And as a bonus, it would be nice if the software designed to improve the performance would work under various UNIX flavors (Solaris, Digital Unix, Linux) as well as under WindowsNT.

### **P**ROGRAMMING MODEL

The Swiss-Tx machine is a distributed memory architecture. Current implementation of shared memory models over distributed hardware are expensive and do not deliver higher performance for middle grain and small grain parallel applications [8, 18]. In fact, to achieve scalable performance, the programmer must handle data decomposition, allocate data subsets to the various nodes in the architecture and specify explicitly data transfers between the nodes of the architecture. Hence the selection of a distributed memory programming model and the use of a message passing interface for parallel programming. The standard message passing API (Application Programmer Interface) is MPI [4,7].

#### **I/O** DESIGN AND LIBRARY INTERFACE

I/O is a major bottleneck in many parallel applications. The main reason for poor application-level I/O performance is that I/O systems are optimized for large accesses, whereas parallel applications typically make many small I/O requests [1,2,9,12,16]. Leaving each parallel program thread to fend off for itself results in poor performance, as each thread performs comparatively small I/O requests, each incurring a high latency (see table 1). Much research has demonstrated the efficiencies of data organization and collective I/O [4,10,14], In the MPI-IO interface, data types take care of data organization, and the API supports non-collective, collective, blocking and non-blocking operations. The Swiss-Tx project has selected the MPI-IO API as an interface to the striped file package.

# THE CAP COMPUTER-AIDED PARALLELIZATION TOOL

To extract maximal performance from commodity component based architectures, and overcome the high latency of their communication network, it is necessary to overlap processing, communication, and data accesses. Writing such asynchronous parallel programs is tedious and errorprone. To facilitate the development of such programs, we ĥave developed a computer-aided parallelization tool, CAP, and parallel file system components. CAP lets us generate parallel server applications automatically from a high-level description of threads, operations and the macro-dataflow between operations. Because of CAP's macro-dataflow nature, the generated parallel applications are completely asynchronous, without the need for callback functions. Each thread incorporates an input token queue, ensuring that communication occurs in parallel with computation. In addition, the CAP runtime environment executes diskaccess operations asynchronously, also without the need for explicit callback functions [6].

We used the CAP tool in several applications, such as the Visible Human Slice Server which offers access to slices and surfaces within the 3D Visible Human dataset (13GBytes), and the RadioControl radio-rating project which correlates the content of radio programs with the content of wristheld audio-data recorders (*http://www-imt.unine.ch/Radiocontrol*). Thanks to CAP the generated applications are flexible; it is easy to maintain and modify the parallel programs. Evaluation of the access times for the applications shows that their performance is close to the best that the underlying hardware can sustain [6]. The CAP tool is also used in a commercialization effort by A2I (*http://www.axsnow.com/*), aiming at providing components for manipulating large raster images.

While the development focus of the laboratory is on WindowsNT, the CAP tool is available on both WindowsNT and UNIX (Solaris, Digital). Among future developments is a wizard for specifying graphically the macro-dataflow between operations.

#### THE SWISS-TX I/O SOFTWARE DESIGN

As a part of the Swiss-Tx effort, the authors implement a portable striped file package called NAFS (Not A File System). To the user, a NAFS striped file is a linearly organized set of bytes. The operations available to manipulate the files are the traditional file operations: create, open, close, delete, read from, and write to a NAFS file at specific offsets. The NAFS files are accessible both through an MPI API and an NAFS API. The aim of NAFS is to make the use of striped files as transparent as possible. To achieve this aim, the NAFS project will provide utilities to move, copy, and display (UNIX cat command) files. Both the NAFS and the MPI API hide the striping to the programmer. The striping information can be made available to the programmer who wishes to take advantage of the information to improve performance.

In the following paragraphs we address the following issues: performance considerations,

- striping and programming interface,

- miscellaneous design issues (need for dedicated I/O threads, network requirement, pipelining, file protection, redundancy),

- the implementation of NAFS using CAP,

- the current status of NAFS.

The CAP language extension is described in a separate box.

#### EXPECTED PERFORMANCE

|                            | port to port<br>bandwidth<br>(Ethernet) | port to port<br>bandwidth<br>(T-Net/MPI) | local-disk<br>throughput |

|----------------------------|-----------------------------------------|------------------------------------------|--------------------------|

| latancy                    | 500ms                                   | 12µs                                     | 10ms                     |

| throughput<br>(nominal)    | 12.5MB/s                                | 100MB/s                                  | 8MB/s                    |

| throughput<br>(aggregate)  | 100MB/s                                 | 1GB/s                                    | 512MB/s                  |

| throughput<br>(2KB block)  | 5MB/s                                   | 62.5MB/s                                 | 0.195MB/s                |

| throughput<br>(50KB block) | 7.5MB/s                                 | 97MB/s                                   | 2.5 to<br>5MB/s          |

#### Table 1 – Performance figures for the Swiss-T1 architecture

Table 1 presents the relevant performance figures for the Swiss-T1 architecture. We consider that each box in the architecture contains two processors and two disks. The measured Ethernet bandwidth per box is 5 to 8 MB/s per box. The nominal T-Net throughput is 200MB/s (100MB/s each way), shared between 4 boxes, or 50MB/s per box. We assume that both the Ethernet crossbar and the T-Net crossbar offer sufficient bandwidth to sustain the nominal throughputs at the box level. The next two paragraphs evaluate the distributed I/O design, and the centralized-server design.

In the distributed I/O architecture that we have chosen, each dual-processor box is both a producer and a consumer of data in an I/O operation. The processors produce data that is consumed by the disks. In a typical balanced I/O transfer, each box spends half the time sending data and half the time receiving data. Hence half the network bandwidth is available for distributed I/O operations. Assuming enough disk bandwidth, the I/O operations can be performed at the rate of 2.5 to 4MB/s per box through Ethernet, and 25MB/s per box through T-Net. In the case if the 32-box T1 architecture, the peak network throughput for I/O is 80 to 128MB/s through Ethernet and 1GB/s through T-Net. The nominal disk throughput is between 2.5 and 5MB/s for 40KB blocks depending on the locality of the data on disk. In the case of a 32 box architecture with 2 disks per box, the peak disk throughput is 160 to 320MB/s. This back-of-the-envelope analysis suggests that the Ethernet bandwidth is below the disk bandwidth, and that it is therefore necessary to use the T-Net for distributed I/O operations in order to achieve the maximum throughput.

These considerations suggest that the distributed approach offers high performance at low cost, if the T-Net is used. The Ethernet-based distributed design offers only acceptable performance. The back-of-the-envelope calculations in this section must of course be validated through experiments, and the overhead of various protocols (NFS, TCP sockets) taken into accounts.

# NAFS DESIGN

In this discussion we assume that a parallel program consists of threads. Whether there are multiple user threads per processes as in CAP or a single user thread per process as in many MPI implementations is not important at this point in the discussion of the design. A striped file consists of one or more *subfiles*.

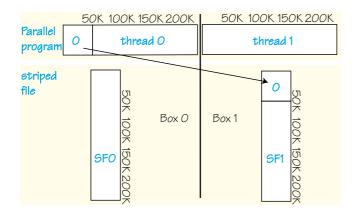

| Fig. 2 – File | striping |

|---------------|----------|

|---------------|----------|

Each NAFS striped file consists of a metafile and one or more subfiles. The striped file is divided in extents (i.e. contiguous data sets of sufficient size to make a disk access worthwhile, typically 50KB) which are stored in subfiles in round robin fashion. A set of extents located at the same position in each subfile is called a stripe. Consider (Fig. 2) a program consisting of a single thread which dumps the content of its memory (a single 1MB block) to striped file userfile.nafs with two subfiles /scratch/p0/ userfile.sub0 (short name: SF0) and /scratch/p1/userfile.sub1 (short name SF1) and an extent size of 50KB. Striped file bytes [0-50K[ are stored in SF0[0-50K[, striped file bytes[50K-100K[ are stored in SF1[0-50K[, striped file bytes [100-150K[ are stored in SF0[50-100K[, striped file bytes [150-200K[ are stored in SF1[50-100K[, etc..

The metafile contains the number of subfiles, the extent size, the total file size and the list of subfile names (absolute OS paths, accessed through NFS on Unix machines or UNCs under WindowsNT). The metafile and subfiles are native OS files, for portability reasons. Each byte in the striped file is described by its offset (64-bit) and value.

When multiple threads are involved in writing to a striped file, each of them writes its own blocks to the file. The number of subfiles in the striped file need not be equal to the number of threads in the parallel program. Multiple requests to the same subfile are serialized. At the NAFS level, the operations read from and write to the striped file a *block-list*, each block being characterized by a size, an offset in the file, and a pointer in memory to the data to be transferred from/to disk. Arbitrary number of threads can take part to collective read/write operations. MPI I/O uses communicators to indicate the threads involved in collective operations, and datatypes to indicate the layout of data both in file and in memory. A software layer transforms MPI communicators and data types into block-lists and sets of threads.

# NAFS ISSUES

Miscellaneous issues must be addressed in the design of the NAFS striped file package: the number of threads per dual-processor box, the high-speed network support, the pipelining of data transfers and disk accesses, the protection of files against multiple simultaneous accesses, and redundancy.

### One dedicated I/O thread per I/O node

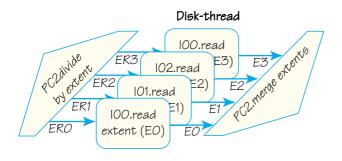

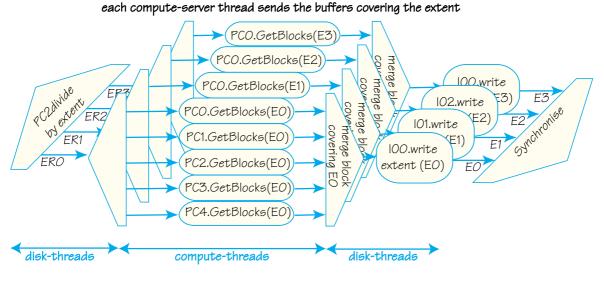

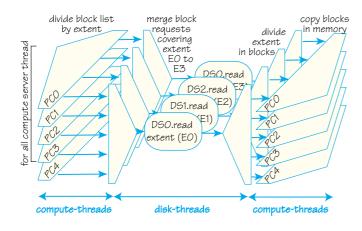

In the distributed I/O architecture, each user thread can request I/O operations from any dual-processor box in the architecture. In effect, it is acting as a client requesting I/O services. It is therefore necessary that each dual-processor box runs a thread dedicated for serving I/O requests from user threads. In this paper, we refer to user threads as compute-threads and I/O-request-serving threads as diskthreads.

# Ethernet/socket communication vs. T-Net/MPI communication

The analysis of paragraph *Expected performance* suggests that it is necessary to use the T-Net to sustain the disk throughput of the distributed I/O design. And the comments of the previous paragraph indicate it is necessary to have a dedicated I/O thread in addition to the usual processing thread(s) in each box. However, many high-performance versions of MPI are not multi-threaded, and

#### **CAP** EXTENSION LANGUAGE OVERVIEW

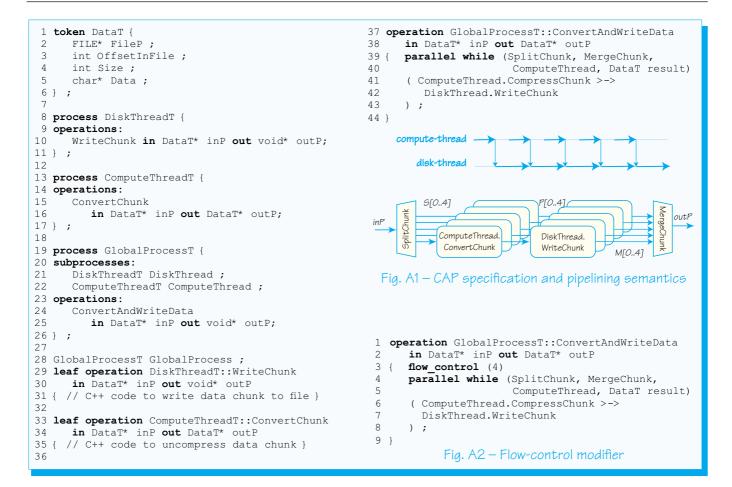

This section presents a simple example describing the basic features of the CAP language extension to C++. CAP's main design goal is to implicitly implement asynchronous parallel behavior. To achieve these goals, it uses language constructs (1) to specify and group threads, (2) to specify the data structures exchanged between threads, (3) to specify the operations the threads and thread groups can perform and (4) to specify the macro-dataflow (pipeline/parallel scheduling) between thread operations.

We first illustrate the asynchronous semantics of the CAP. Consider a CAP program which converts data on one processor and writes it to one disk, chunk by chunk. For the sake of simplicity, we assume that the conversion operation does no change the size of the data chunk, nor does it require data in other chunks. Fig. A1 shows the syntax, graphical representation and timing diagram of such a program. In Fig. A1, program lines 1 to 6 specify the data structures specifying the data chunks moved between the program's two threads. Lines 8 to 17 specify the two threads (DiskThreadT, ComputeThreadT) in the program and the operations they can perform (WriteChunk and ConvertChunk respectively). Lines 19 to 26 logically group the two threads under the name *GlobalProcessT*, and specify which operation(s) they can perform as a group (*ConvertAndWriteData*). Line 28 instantiate *GlobalProcessT*, which automatically creates the two threads under the *GlobalProcessT* umbrella. In CAP, threads are instantiated upon program initialization. No threads are created during program execution, thereby reducing execution overhead.

Lines 29 to 44 specify the behavior of the program. The input of the program is a *DataT* token initialized with an open file descriptor FileP, an OffsetInFile, and a Data pointer to the memory data. The asynchronous parallel semantics of the CAP language is entirely handled by the parallel while expression (lines 39 to 44). The SplitChunk C++ function (passed as parameter to the parallel while expression) incrementally divides the *DataT* input token *inP* into several *DataT* tokens referencing consecutive 50KB blocks in memory. The *ComputeThread* converts the data chunks one after the other, and forwards each converted token to the DiskThread as soon as it is converted. The DiskThread writes the *P[i]* tokens to disk one after the other, and generates the *M*[*i*] void tokens. As soon as each of the M[i] tokens is available, it is merged by the MergeChunk function (not shown) into the outP void token. When all tokens have been merged, the *ConvertAndWriteData* operation is complete.

The graphical representation of the ConvertAnd-

WriteData operation (bottom of Fig. A1) matches the textual specification. It indicates that the input token is divided using the split function into several data chunks that are fed to the *ComputeThread*'s *ConvertChunk* operation. The output of the conversion is fed to the *DiskThread*. WriteChunk operation. The output of the WriteChunk operations are used for synchronization purposes: when all outputs have been received, the *ConvertAndWriteData* operation is complete.

The *SplitChunk*, *MergeChunk* functions and the *WriteChunk*, *ConvertChunk* operations are all executed asynchronously, i.e. provided enough processors and disk they could all be executed simultaneously (albeit on different data chunks). It is possible to allocate the *DiskThread* and the *ComputeThread* not only on different processors in the same box, but also on different boxes. In that case, the token transfer over the network is automatic and asynchronous, that is, computation, communication and disk accesses are overlapped.

In the case where the split function generates many chunks of data, there is a risk of memory overflow, since the split function is typically much faster than the conversion operation. To work around this, CAP uses flow control modifiers to its parallel construct, limiting the number of tokens simultaneously active inside the parallel construct. Fig. A2 shows a modified ConvertAndWriteData where the number of simultaneously active data chunks is limited to 4.

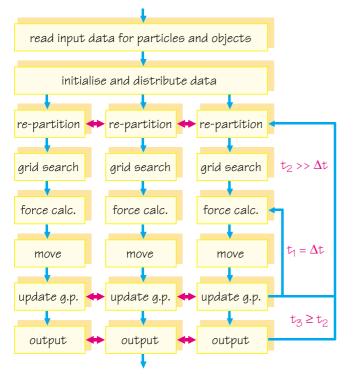

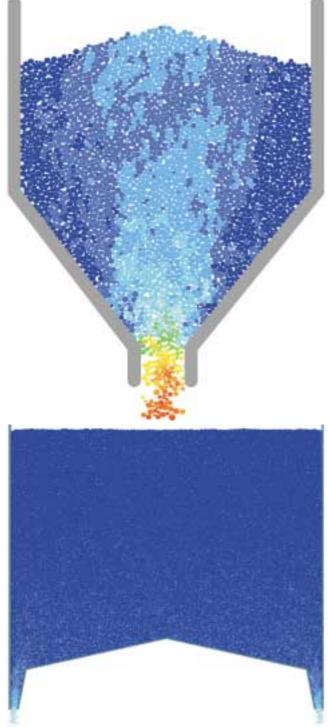

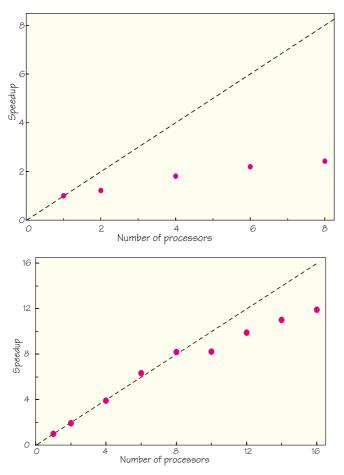

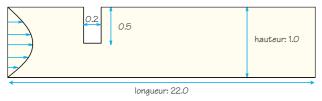

To achieve asynchronous parallel behavior in CAP, the programmer replaces the disk- and compute-thread (lines 21 and 22) by arrays of disk- and compute-threads (e.g. DiskThreadT DiskThread[MAX] and ComputeThreadT ComputeThread[MAX]). The pipelining behavior explained in the previous paragraph is still available, but up to MAX data chunks can be compressed or written simultaneously, depending on the available hardware resources. The work of the CAP programmer is then to define the tokens and the operations required to achieve a given algorithm. The CAP language extension supports 8 predefined expressions, 3 for asynchronous parallel behavior (parallel, indexed parallel, parallel while), 3 expressions for iterative behavior (sequence, for, while), and 2 expressions for branching (if, ifelse). CAP programs based on predefined CAP expressions are deadlockfree by construction. CAP programs are reconfigurable without recompilation: the same executable can run on a 1-processor 1-disk low-end PC, on a 4-processor 4-disk shared-memory machine, or on an 10-processor distributed-memory architecture with 60 disks.